stm32plus::net, PHY module

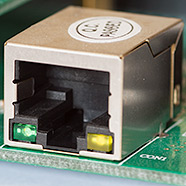

The ethernet PHY is responsible for the transmission and reception of frames on the network. The PHY is very closely tied to the MAC and supports one or both of the MII and/or the RMII interfaces.

PHY implementations

stm32plus::net comes with support for two PHYs, the DP83848C from Texas Instruments and the KSZ8051MLL from Micrel. Here’s an example of a physical layer configuration using each of them:

typedef PhysicalLayer<DP83848C> MyPhysicalLayer;

typedef PhysicalLayer<KSZ8051MLL> MyPhysicalLayer;

Configuration parameters

The following parameters are made available in the stack’s configuration object for customisation:

// station address (default is 1) uint16_t phy_address; // read timeout in ms (default is 1000) uint16_t phy_readTimeout; // write timeout in ms (default is 1000) uint16_t phy_writeTimeout; // time to wait for a link in ms (default is 1000) uint16_t phy_linkTimeout; // time to wait for auto negotiation in ms (default is 1000) uint16_t phy_autoNegotiationTimeout; // time to wait after manual config is complete (default is 10) uint16_t phy_postConfigurationDelay;

Methods exposed

All methods return true if they worked, or false if they fail. If they fail then the global errorProvider object is updated with the failure detail and an error event is fired.

bool phyEnableInterrupts(uint8_t interruptMask) const; bool phyDisableInterrupts(uint8_t interruptMask) const; bool phyIs100M(bool& is100) const; bool phyIsFullDuplex(bool& isFull) const; bool phyClearPendingInterrupts() const; bool phyGetPendingInterrupts(uint16_t& interrupts) const;

If the PHY supports interrupt-based notification of events (and both the DP83848C and the KSZ8051MLL do) then you can use phyEnableInterrupts to enable a group of interrupts. The interrupt(s) to enable are specified by the bitmask parameter. See the source code for the supported interrupt masks.

Conversely, phyDisableInterrupts can be used to disable some interrupts and phyClearPendingInterrupts must be used in your IRQ handler to ‘acknowledge’ the interrupt so it won’t keep on firing over and over.

phyGetPendingInterrupts can be used to read the interrupt-pending register from your IRQ handler to find out which of the interrupt(s) have fired.

Any use of the PHY interrupts will require you to wire up the interrupt pin provided by the PHY to a GPIO pin on the STM32. You should then enable EXTI on that pin and subscribe to interrupts from it. Several of the examples use this facility to subscribe to link-down interrupts from the PHY.

phyIs100M is used to detect if the PHY has connected with its link-partner at 100Mb/s. true indicates 100Mb/s, false indicates 10Mb/s. We don’t support any of the Gb ethernet modes.

phyIsFullDuplex indicates whether the PHY has connected with its link-partner in full-duplex, collision-free mode or the legacy CSMA/CD half-duplex mode. true indicates full-duplex, false indicates half-duplex.